Table of Contents

Circuits Combinatoires & Séquentiels

Nota Bene : Cette page utlise le plugin Dokuwiki pour écrire des fomules mathématiques en Latex (syntaxe).

Logique Combinatoire

Les fonctions logiques élémentaires qu'il est possible de mettre en oeuvre sur le silicium (en combinant des transistors) sont les portes NAND et NOR. Plus de détails.

Voici la représentation classique de ces portes :

Et leur table de vérité :

| a | b | NAND | NOR |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

Soit $+$ l'opérateur or et $.$ l'opérateur and. On utilise le symbole $\bar{x}$ pour la négation de $x$. La fonction logique nand (resp. nor) est dite complète, car toute fonction logique (ou circuit) peut être implanté uniquement au moyen de cette porte, en en combinant plusieurs. Le nombre d'étages nécessaire conditionne la durée de propagation du circuit.

Voici quelques exemples d'utilisation de la porte NAND, pour réaliser divers fonctions logiques :

\begin{eqnarray*}

\bar{x} &=& \overline{x.x}

x.y &=& \overline{\overline{x.y}}

x+y &=& \overline{\bar{x}.\bar{y}}

x \oplus y &=& \overline{ \overline{(x.\bar{y})}.\overline{(\bar{x}.y)}}

\end{eqnarray*}

Pour prouver ces résultats, il faut utiliser propriété $\overline{\bar{x}} = x$, ainsi que la loi de De Morgan :

\begin{eqnarray*}

\overline{x+y} &=& \bar{x}.\bar{y}

\overline{x.y} &=& \bar{x}+\bar{y}

\end{eqnarray*}

La fonction logique XOR (ou exclusif, opérateur $\oplus$) a pour table de vérité :

| a | b | XOR |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

En particuler, XOR a quelques bonnes propriétés :

- associatif

- $x \oplus y \oplus z \oplus …$ calcule la checksum dite du bit de parité.

- $x \oplus y = \bar{x}.y + x.\bar{y}$

Circuits Combinatoires

- Un multiplexeur (MUX) est un circuit qui sélectionne une entrée $E$ parmi $m=2^n$ fils à partir d'une entrée de sélection $S$ à $n$ bits (ou plutôt $n$ fils) et la propage sur le fil unique de la sortie $Z$. On note m:1 mux un multiplexeur m-vers-1 avec n bits de sélection. Par exemple, un mux 8:1 aura une entrée S à 3 bits.

- Le plus souvent, nous aurons uniquement besoin d'utiliser un mux 2:1 contôlé par une entrée logique $S$ sur 1 bit (ex. un interupteur on/off). On dispose donc de deux entrées $E_0$ et $E_1$. Si $S=0$, on sélectionne $E_0$ comme sortie ($Z=E_0$), sinon on sélectionne $E_1$ ($Z=E_1$) à la manière d'un interrupteur dans un circuit va-et-vient.

- Un démultiplexeur (DEMUX) effectue l'opération inverse. C'est un circuit qui permet d'envoyer une entrée unique $E$ sur une sortie $Z$ parmi $m=2^n$ en fonction de l'entrée de sélection $S$ à $n$ bits. On note 1:m demux un démultiplexeur 1-vers-m avec n bits de sélection. Par exemple, un demux 1:8 aura une entrée S à 3 bits.

- On considère le multiplexeur comme un multiple-input, single-output switch et le démultiplexeur comme un single-input, multiple-output switch.

- Un décodeur à $n$ bits est un démultiplexeur 1:m simplifié tel que $E=1$ (avec $m=2^n$). Plus précisément, il prend une entrée de sélection $S$ sur $n$ bits et produit une sortie $Z$ sur $m=2^n$ bits, tous à zéro à l'exception de la sortie $Z_j$ dont l'indice $j$ correspond au codage binaire sur l'entrée $S$. Considérons par exemple, un décodeur 3-vers-8 ($n=3$ et $m=8$). Si l'entrée S vaut $110$ en binaire, seule la sortie $Z_6$ sera à 1.

- Un codeur $n$ bits effectue l'opération inverse du décodeur : il suppose qu'une seule entrée parmi $m=2^n$ vaut $1$ et produit en sortie le numéro de cette entrée, codé en binaire. On utilisera plus rarement ce circuit.

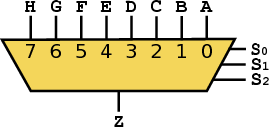

Voici un exemple de représentation d'un mux 8:1.

La table de vérité simplifié de ce circuit est :

| $S=S_2S_1S_0$ | Z |

|---|---|

| 000 | A |

| 001 | B |

| 010 | C |

| 011 | D |

| 100 | E |

| 101 | F |

| 110 | G |

| 111 | H |

Logique Séquentielle & Circuits Séquentiels

- La bascule SR, bistable…

- La bascule (flip-flop en anglais) est une mémoire synchrone dépendant d'une entrée clock (ou horlge). L'horologe produit un signal périodique en créneau.

- En particulier, la bascule D (pour Data) est une mémoire 1 bit. Cette bascule recopie son entrée D sur la sortie Q sur le front montant de l'entrée C ou clock. Durant toute la durée d'un cycle, Q conserve sa valeur.

- Un registre est un ensemble de bascule D fonctionnant en parallèle.

- On utilise un unique et même signal clock pour tout le circuit. Attention à ne pas faire de combinatoire avec le signal clock. La traversée de portes logiques risquerait de désynchroniser ce signal !

- La période de l’horloge doit être compatible avec le temps de propagation de la logique combinatoire.

Simulateur de Circuit en JavaScript

Attention à bien distinguer dans la bibliothèque de composants, ceux qui manipulent des fils simples et ceux qui manipulent plusieurs fils (bus x4). Il faut donc relier des sorties simples sur des entrées simples, et des sorties bus x4 sur des entrées bus x4. De même, il faut veiller à respecter le sens : on branche les sorties blanches sur les entrées jaunes. Sinon ça ne marche pas du tout ! Les composants BusIn et BusOut permettent de relier des entrée simples avec des sorties bus x4 et réciproquement.

Quelques Exemples